是青出于蓝还是江河日下 Prescott全面解析

-

面对AMD64,Intel新P4奋起反击

2003年后期,为了暂时压制AMD公司新推出的Athlon64系列处理器,Intel不惜工本在旧有的P4核心基础上,增加2MB三级缓存,推出了价格高昂的P4至尊版(3.2GHz频率的该型号处理器,千片采购价就高达700多美元)。但仅凭这样的高价处理器,在主流市场显然是站不住脚的;而旧有的Northwood核心P4在面对Athlon64系列CPU的威胁时,在某些应用中已经略显疲态。

在原有的P4架构基础上,要再一次夺取先机并保持处理器的制作成本在可接受的范围之内,就必须进一步改进P4处理器的内部架构和制作工艺。这样才可能通过提升处理器的工作频率,在新一轮的CPU大战中站稳脚跟。

2004年2月1日,Intel终于推出了举世瞩目的90nm制程P4E(Prescott核心P4)系列处理器。首批推出的Prescott核心P4处理器共有4款,分别为:P4 2.8A、P4 2.8E、P4 3.2E以及P4 3.4E。其中P4 2.8A前端总线数据传输频率仅为533MHz,并且不支持超线程技术,以后缀“A“来标识。而其余的型号均为800MHz前端总线数据传输频率,都开启了超线程功能,以后缀“E“标识。

那么,此款处理器对P4处理器原有的Netburst架构究竟作出了什么改进,使用了哪些新的处理器制造技术,会不会如Athlon64系列那样加入64位扩展,初期推出的几款处理器实际的性能表现又会如何呢?以下,我们就为大家一一揭开谜底。

新技术热点分析:超长的流水线级数

在我们的上一篇文章中,我们已经看到AMD K8核心处理器为了进一步提升频率,将流水线级数由K7的10级增加到了12级。而在Prescott核心的P4处理器中,为了进一步提升处理器的频率,Intel把Trace Cache之后的流水线级数变本加厉,由以前的20级增加到了30级。这恐怕是此款处理器最引人注目的改变之一了,也因此引来了诸多媒体的议论。

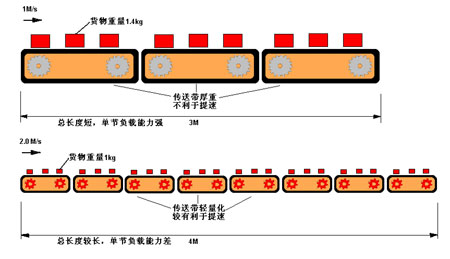

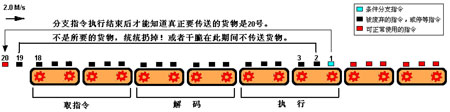

我们都知道,处理器流水线基本可以划分为:指令取→指令解码→指令执行→载入/储存→写回寄存器这五个部分。通过这样的流水线设计,就可以在每条流水线上同时处理一条以上的指令。为了叙述方便,我们可以把流水线假想为一组传送带,如下图:

处理器长短流水线示意图

短流水线好比节数较少,单节皮带行程长的模式。它的单节皮带负载能力更大。而长流水线则好比节数较多,单节皮带行程短的模式。它的单节皮带负载能力较弱。

虽然从长度上看,由于长流水线级数较多,因此行程也较远,在皮带传送速度相同(均为1M/s)的情况下,当然是短流水线占优势。但随着工厂技术的发展,必须提高产量。此时我们就需要提高传送带的送货量。显然我们可以想到最简单的方法就是增加皮带的传送速度。

然而在短流水线的传送带中,由于单节皮带较为粗长,本身质量较大,因此要进一步提速就显得十分困难(极限速度可提升到1.2M/s)。相比之下长流水线设计的传送带则由于单节皮带质量小,提速就显得容易得多(极限速度可提升到2M/s)。这样我们通过给长流水线传送带大幅度提速,在流水线各环节同时正常运转的情况下,实现了超越短流水线传送带的目的。

显然,如果在此基础上进一步增加并行传送带的组数,构成“超标量“传送带,那么长流水线的速度优势还将得到更好的体现。

由于上述的优点,多数处理器在升级换代时,基本都采取了增加流水线级数的策略,以下,我们给出Intel公司几款具有代表性处理器的流水线布置图,以供大家参考。

Intel系列处理器流水线级数简图

需要注意的是,P4系列处理器的流水线级数尚不包括前面的取指令、解码部分。通过增加流水线的级数,Intel宣称Prescott核心P4处理器的工作频率将可达到5GHz左右。

但是凡事有利必有弊。首先,长流水线的优势必须在提速到达一定程度之后才能够体现出来。可是处理器厂家在长流水线处理器推出的初期,由于市场等多方面因素,又不可能马上以较高的频率推出新处理器。因此,这些处理器在某些条件下自然就会出现不尽人意的情况。其次,Prescott的超长流水线设计和较高的频率,也将带来其它方面的一系列问题。为了减小这些问题可能带来的损失,在Prescott中,Intel采取了许多措施进行补救。下面,我们就进一步为大家说明。

新技术热点分析:改善内存延迟问题

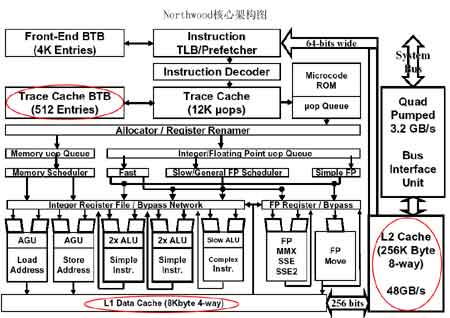

要分辨两栋建筑物的异同,没有内部构造图是不行的,对于处理器来说也是如此。所以,首先我们还是来看两张Prescott核心架构与Northwood的架构对比图吧:

Prescott与Northwood的架构对比图

我们可以看到,上图中最明显的变化有三处:

◎指令追踪缓存(Trace Cache,作用类似于以前的一级指令缓存)所用的分支目标缓存(Trace Cache BTB,主要用于动态分支预测),条目数(Entries)由512条增加到2000条;

◎一级数据缓存容量倍增,由原来的8KB增加到了16KB。缓存联合路数也随之倍增,由原来的4路联合(4ways)增加到8路联合(8ways);

◎二级缓存容量也由原来的512KB增加到了1MB,缓存联合路数则保持不变。

考虑到读者对于缓存已经比较熟悉,因此我们先就涉及到缓存变化的后两个项目进行分析。而对于大家还不太熟悉的BTB,我们将放到后面再作说明。

前面我们已经提到,Prescott的频率可高达5GHz左右,而归根结底,处理器需要内存为其输送数据。处理器在如此高的频率下工作,即使是尚未走向主流的下一代DDRⅡ内存,在没有辅助措施的条件下也会略显吃力,更不必说目前的DDR内存了。

内存系统跟不上处理器的脚步,是长久以来存在于系统设计中的一个问题。对于这个问题,AMD公司通过在K8处理器中内置内存控制器,并增加二级缓存容量到1MB来解决。而同期推出的P4至尊版则没有变动其它机构,仅追加了2MB三级缓存。至于Prescott,则主要采用了以下三个方面的措施进行解决。

●最容易理解的措施――增加一级、二级缓存的容量。我们已经从对比图中看到了。不过需要提醒大家注意的是,虽然增大缓存的容量有利于缓解慢速的内存所带来的影响,但在某种条件下,也可能随之提高缓存的延迟,在Prescott中就出现了这种现象。以下就是我们使用ScienceMark 2.0测试缓存延迟时所得到的结果。

表中可见,扩容后,Prescott的一级缓存、二级缓存延迟分别增加到Northwood的2倍和1.4倍左右,扩容的副作用较为明显。

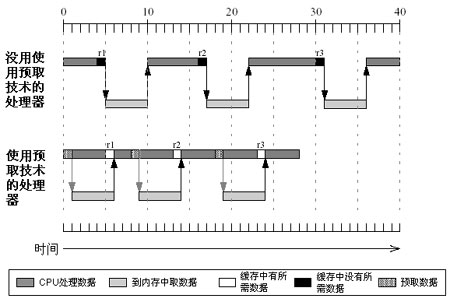

●第二条措施――对P4原有的预取技术作出改进。

考虑到读者可能对预取技术还比较陌生,因此我们首先对预取技术作简要的说明。没有使用预取机构的处理器,只能在需要对数据进行处理时查找缓存,如果缓存中没有所需数据,就必须停止工作,等待内存提供此数据。而使用预取机构后,则可以在数据需要处理之前就完成查询缓存,向内存中取数据,并将数据预取到缓存中工作,隐藏了内存的延迟,如下图:

预取原理图

P4中具备软件预取和硬件预取两种预取方式。所谓软件预取,就是在程序的代码中由编程人员人为地添加预取指令。而硬件预取则由处理器全权管理预取工作,不需要编程人员手工插入预取指令。Prescott中对两种预取都做出了一些改进。

软件预取方面,对过去的P4来说预取的对象只能是普通数据。这意味着软件预取指令只能为二级缓存提供预取服务。而在Prescott中则扩大了软件预取的对象,不仅可以为二级缓存提供预取服务,而且还能够为另一种重要的缓存――二级缓存D-TLB提供预取服务。

此外,在旧的P4中,软件预取指令必须由速度慢的MicrcodeROM负责解码。而现在则可由速度较快的硬件解码器解码,存放在发布速度快得多的Trace Cache中。也算提高预取性能的一种辅助措施吧。

硬件预取方面,Prescott的硬件预取机构在预取时机、预取对象的选择上也变得更加智能化,不过Intel对于硬件预取方面的改变并没有提供更多的细节说明。

●最后由于Prescott中超线程技术的存在,对弥补内存延迟的技术提出了更高的要求,为此,Intel进一步增加了部分内部缓冲器的容量,以满足开启超线程时的需要。

新技术热点分析:处理器前端的变化

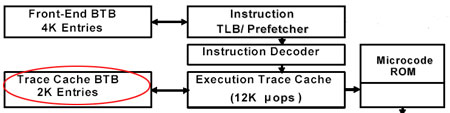

前面我们主要涉及的,只是处理器外围的缓存部分,下面,我们把目光投向Prescott的核心内部,首先看看前端部分的一些变化:

图为:Prescott前端结构

如上图,P4的前端部分主要由指令取、指令解码、追踪缓存、MicrocodeROM以及分支预测机构所组成。在这一部分中,Prescott主要在以下三个方面采取了改进措施。

◎在解码部分,Prescott将把更多的指令将交由硬件解码器进行解码后由指令发布速度为3条/周期的追踪缓存来发布,而不是交由发布速度仅1条/周期的MicrocodeROM来解码后发布,比如我们在上面提到的软件预取指令,就是一个很好的例子;这一点,同Athlon64的情况比较类似,而有关MicrodeROM与硬件解码器的区别,请点击此处察看。

◎第二方面,Prescott的解码部分能够识别出更多指令之间不必要的数据依赖(Data Dependence),以便提高后面的乱序执行效率;

◎最后,也是最重要的一个方面,就是对分支预测机构的改进了,我们将主要针对此方面的改进作一些简要说明。

首先,是我们在前面尚未涉及的Trace Cache BTB部分。必须明确的一点是,Trace Cache BTB部分的变动,与Prescott的动态分支预测机构关系十分紧密,而动态分支预测机构的性能,则对于Prescott这样的超长流水线处理器,具备相当重要的意义。

我们知道,简单处理器取指令时,只能按照编译后的指令静态顺序进行顺次读取;但由于分支指令的跳转特性,打乱了这种依次执行的顺序;如果此时我们仍然按照指令编译时的静态顺序顺次读取,或是在具备分支预测的处理器上出现分支预测失败的现象,错误地读取了其它的指令进行处理,就必然造成流水线部分区域的停工或是作了无用功。如下图:

长流水线分支预测失败示意图

对于Prescott这样的31级超长流水线来说,这样的问题给处理器带来的危害显然比稍短的流水线更大。为了解决流水线在执行条件分支指令时的上述问题,就必须改进Prescott处理器中的分支预测机构,这方面Intel主要有以下三方面的措施:

◎动态分支预测方面,首先就是我们前面提到的,将追踪缓存(Trace cache)所用的分支目标缓冲条目数由以前的512条增加到了2千条;

◎Intel还宣称在原有的动态分支预测机构中加入非直接跳转分支预测器(Indrector Branch Predictor),改进了动态预测非直接跳转分支的能力。

◎第三条措施,就是改进静态分支预测的策略。

新技术热点分析:提高分支预测机构

要理解前页所述的改进,我们就必须首先了解分支预测的一些基本原理。

同大多数处理器一样,Prescott处理器的分支预测机构可以分为动态分支预测机构以及静态分支预测机构两大类,而其中动态分支预测机构由分支目标缓冲(Branch Target Buffer,以下简称BTB)以及预测跳转条件是否满足的动态预测机构组成:

分支预测原理图

图中可见,BTB与我们熟悉的一级、二级缓存十分类似,只不过缓存的对象不同而已,前者缓存了分支指令及其挑转目标的地址,而后两者则缓存具体的数据或指令。在每一个BTB的条目中,集中存储了分支指令地址、跳转地址以及分支指令的跳转历史纪录。需要注意的是,由于P4对于其分支预测机构的细节一直不愿意做过多的透露,因此其中实际的分支预测机构组成状况,与上图所表示的结构必然在细节上存在许多不同之处,但从原理上说,二者是基本相同的。

大致了解了分支预测的原理之后,再回过头来看Prescott中的分支预测改进状况,就较好理解了。

◎动态分支预测方面,与其它处理器不太相同,P4处理器在指令预取单元和Tace Cache单元上,各放置了一套BTB机构,但两套BTB机构的作用和工作原理是类似的。增加BTB条目数,能够纪录的分支指令数就越多,当遇上分支指令较密集,分支指令跳转情况变化较复杂的程序时,将体现出一定的优势。

◎此外,由于分支预测指令中的跳转地址有可能使用变量表示,而不是如我们上面举例的那样总是5、150这样的常数;这种情况我们称为非直接跳转分支(Indirect Branch)。如果此时仍然使用图中的机构,显然将造成BTB的频繁预测失败(储存在BTB中的分支跳转地址可能是不断变化的)。Intel宣称在Prescott的动态分支预测机构中加入由Pentiumn M(Banis)中引用的非直接跳转分支预测功能。这样,就提高了执行非直接跳转分支时的预测成功率。

◎作为动态分支预测的一种侯补方案,静态分支预测的性能对于处理器来说也具备一定的重要性。静态分支预测方面,在过去的P4里,一直奉行以下的原则:

如果分支所跳转的地址为逆向跳转,则静态预测为分支跳转成立,执行跳转;而如果分支所跳转的地址为正向跳转,则静态预测为分支跳转不成立,按照编译顺序读取下一条指令,下图表示了这种静态策略:

图为:Northwood的静态分支预测

的确,在分支循环次数较多的程序中,这样的静态预测方案所得到的预测命中率较高。但是如果遇到的不是循环用分支语句,如果还这样预测就不行了。所幸大多数情况下,分支循环程序所包含的指令数目都比较小(意味着循环跳转的地址偏移量不会很大),因此在Prescott中,Intel在原有的静态分支策略中加入了距离判断算法,仅在所跳转的地址为逆向跳转,且跳转的地址距离分支指令本身的地址偏移量较小时,才执行跳转。下图表示Prescott与旧P4在这方面的区别:

更智能化的Prescott静态分支预测

显然,这样的静态分支预测办法显得比以前所使用的方法更加“智能化”一些。

新技术热点分析:高效乱序执行核心

接下来,我们进入到核心的中部,这一部分主要完成为指令的执行调配所需的资源、动态地编排指令的执行顺序等工作。此部分与后面我们将要提及的运算执行单元部分一起,组成了P4的乱序执行核心。

图为:Prescott处理器乱序执行核心第一部分

在这一部分中,Prescott相比过去的P4,做出了以下三个方面的改进:

◎增加了用于浮点、多媒体运算指令的排序(Scheduler)窗口。排序窗口的增大,有利于发现更多可以并行处理的浮点和多媒体指令,以提高乱序执行浮点和多媒体指令的效率;

◎改良了用于载入(Load)和储存(Store)指令排序的机构,减小了两种指令的相互等待时间;

◎增加与各个指令排序器联用的指令列表缓冲(MemoryμOP Queue以及Integer/Floating PointμOP Queue)的容量,以便缓冲更多由上级的分配/寄存器换名单元(Allocator/Register Renamer)送来的指令,减小上级单元因等待而产生的空闲状况。

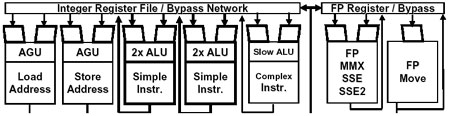

最后是处理器的运算执行单元部分,主要由负责整数运算的ALU、负责浮点和多媒体运算的FPU以及负责地址计算、数据载入以及计算结果储存的AGU部分组成:

图为:Prescott处理器乱序执行核心第二部分

在这一部分中,Prescott相比过去的P4,做出了以下两个方面的改进:

◎在两个快速ALU单元(以两倍于处理器运行频率的速度工作)之一中加入处理移位/旋转操作的机构;而在旧P4中,这部分功能必则由慢速的ALU单元来处理。加入新的移位/旋转操作机构之后,处理此类运算的速度将得到提高;

◎过去的P4,必须依赖浮点单元进行整数乘法运算,这不仅给浮点单元增加了负担,而且还需要把待处理的数据在浮点、整数单元之间相互传递,浪费处理器内部的数据传输带宽。Prescott则添加了单独的整数乘法单元,消除了这些问题。

Prescott相关指令集分析

如果我们把处理器的内部架构比喻为骨架,那么在处理器上使用的指令集,则可以说是处理器的灵魂。任何一款处理器,都必须依靠指令集的帮助,才能够发挥出足够的威力。这一点,只要我们看一看SSE2、MMX或是3DNow!这样的扩展指令集对发挥处理器架构优势所起的作用就会明白。Prescott也不例外。这一次Intel为Prescott专门设计了如下表所示的13条新指令:

通过在程序中使用这些指令,程序员能够更好地发挥Prescott处理器固有的架构优势,进一步提高处理器在多媒体处理、超线程应用等领域的性能表现。

此外,最令人关注的,恐怕就是Prescott处理器是否如AMD的K8系列处理器那样包含64位指令集扩展了。在不久前召开的Intel春季技术峰会上,身为Intel首席执行官之一的Craig Barrett终于亲口承认了这一点。

按照这位官员的说法,今年的第二季度,Intel就将首先在服务器市场推出核心代号为Nocona的处理器,此款处理器与Prescott内部构造基本相同,只不过添加了更大的缓存,并可以支持多处理器配置。并在此款处理器上市后不久再推出单处理器配置的服务器、工作站型Prescott处理器。而微软方面也表示将在不久的将来推出可兼容K8与Prescott处理器的64位操作系统版本。

此外,Intel还提供了用于Prescott核心64位指令集编程的指导书,从这一份指导书中,我们可以看到,Intel在Prescott处理器的64位扩展上,采取了和AMD的K8处理器十分类似的策略,同样提供了寄存器扩展和多种操作模式的支持。其中共包含两种操作模式,其一是传统的IA32模式,其二是可兼容32-64位指令的IA32e模式,各模式的具体状况见下表:

在64位模式下,Intel也对可用的寄存器进行了扩展,如下表所示:

所有这些都意味着目前上市的桌面型Prescott处理器,已经具备了可执行64位指令的功能单元。只不过由于Intel把64位应用局限在服务器、工作站市场,因此没有在眼下推出的桌面型Prescott处理器时中,将这些功能打开或对此隐含功能进行大肆宣传。

Prescott的90nm工艺

一款处理器能否在市场上站住脚,仅靠内部架构以及指令集的设计是远远不够的。设计得再好的产品也必须最终在生产上得以实现;反过来说,优良的生产工艺和生产成本控制技术又可以保证处理器架构设计师们放心地采用更加复杂的处理器设计。

作为首颗采用90nm制程以及可减小电子流动阻力的应变硅技术制作的桌面型处理器。借助于Intel先进的处理器生产技术。性能方面Prescott核心集成的晶体管数和可稳定运行的频率范围得到了显著的提升,成本方面处理器的核心面积也得到了较大幅度的缩减,这一点,我们从如下的一组对比图表中就可以清楚地看出来:

然而,尽管使用了新工艺新材料制作。初期推出的Prescott还是给我们带来了少许的遗憾,它夸张的功耗参数,使它成为桌面处理器的发热之王。

TDP值越高,意味着处理器所需要配备的散热器规格也越高。我们希望随着工艺的改进,在下一个制程步进号的Prescott中,发热量过大的问题能够得到某些程度的改善。

Prescott面对面的大探询

说了那么多原理还是让我们轻松一下,来看看Prescott处理器和其老前辈Northwood以及死敌Athlon64 3200+的正面、侧面合影图:

图为:Prescott、Northwood以及Athlon64 3200+合影

从正面和侧面来看,Prescott相比过去的Northwood,在整体尺寸以及外形上并没有什么明显的区别。而由于内置了内存控制器,Athlon64 3200+则在体形上显得“粗壮”一些。

图为:Prescott、Northwood以及死敌Athlon64 3200+的合影

而从背面图的对比来看,Prescott底部用于核心电压滤噪的电容数目相比Northwood增加不少,排列方式也发生了较大的改变。根据我们的猜测,这可能是由于Prescott核心工作电压相比Northwood降低了不少,因此对电压的稳定度也有了较高的要求使然。相比之下,Athlonj64 3200+处理器则由于背部针脚数较多,因此把滤噪电容都放置在了处理器的正面。

看过了处理器的外观,让我们进一步使用Cpu-Z软件,来观察一下处理器内部参数的变化:

从Cpu-Z 1.21中,明显可以看出,正如我们在前面的分析中所说的,Prescott的一级、二级缓存容量都相比Northwood得到了倍增。除此之外,我们也可以看到,Prescott处理器的CpuID号为0F33,而D1制程的Northwood则为0F27。遗憾的是Cpu-Z最新的1.21版本仍然不能识别出Prescott的制程步进号。而根据Intel相关资料显示,我们收到的此款Prescott制程步进号应为C0,算是作为对Cpu-Z信息的一条补充吧。

PCPOP-电脑时尚 文/小胖胖

相关视频

相关阅读 Windows错误代码大全 Windows错误代码查询激活windows有什么用Mac QQ和Windows QQ聊天记录怎么合并 Mac QQ和Windows QQ聊天记录Windows 10自动更新怎么关闭 如何关闭Windows 10自动更新windows 10 rs4快速预览版17017下载错误问题Win10秋季创意者更新16291更新了什么 win10 16291更新内容windows10秋季创意者更新时间 windows10秋季创意者更新内容kb3150513补丁更新了什么 Windows 10补丁kb3150513是什么

- 文章评论

-

热门文章

谷歌眼镜拆解详细图

谷歌眼镜拆解详细图

最新文章

Intel 12代酷睿低功耗

Intel 12代酷睿低功耗 AMD RX 6500显卡价格多

AMD RX 6500显卡价格多

Intel ARC A380性能规格曝光 显卡ARC A380最小米12发布会在哪看 小米12新品发布会直播地小米9 Pro 5G手机价格 小米9 Pro 5G手机什么iPhone 11发布会直播地址 iPhone 11发布会中

人气排行 SSHD固态混合硬盘详细介绍三星Galaxy Alpha S7拆解图文教程 三星Gala软超频卷土重来――ClockGen全攻略cpu天梯图2013最新(7月)桌面超频人人都行 升技AI7主板之终极测试小米路由器3怎么样 小米路由器3配置评测小米笔记本Air玩游戏怎么样 小米笔记本Air玩一起来看世界上最昂贵的电脑机箱吧

查看所有0条评论>>